建材制品模具 建筑建材生產的關鍵支撐

在現代建筑行業中,建材制品模具扮演著不可或缺的角色,它是實現各類建筑建材精準制造的核心工具。模具通過標準化的設計,能夠確保建材產品尺寸一致、形狀規范,有助于提升建筑的整體質量和施工效率。

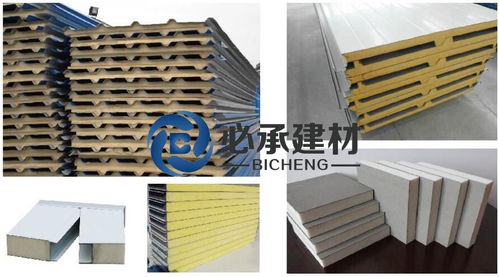

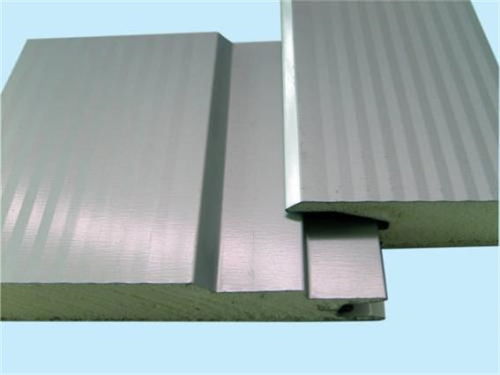

從應用領域來看,建材制品模具廣泛應用于混凝土預制構件、磚塊、裝飾材料等生產中。例如,混凝土墻板模具可實現大規模快速生產,滿足工業化建筑需求;路面磚模具則幫助制造出美觀耐用的鋪裝材料。這些模具不僅提高了建材生產效率,還在保證產品一致性的降低了制造成本。

隨著建筑行業向綠色、智能化方向發展,建材制品模具技術也在不斷革新。新型材料如復合材料模具的應用延長了模具使用壽命,而數字化設計和3D打印技術則為定制化、復雜結構建材的生產提供了可能。模具行業將繼續與建筑建材產業協同創新,推動建筑行業向更高效、環保、高質量的方向邁進。

如若轉載,請注明出處:http://m.fzz8.cn/product/48.html

更新時間:2026-04-13 23:09:22